### EVALUATION KIT AVAILABLE **CVBS/S-Video Filter Amplifier with** SmartSleep and Bidirectional Video Support

#### **General Description**

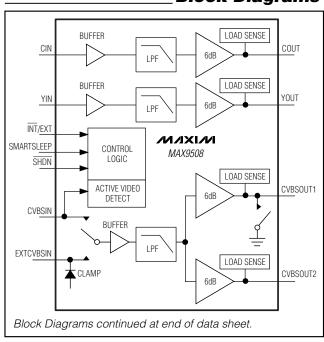

The MAX9508 video filter amplifier with SmartSleep and bidirectional video support is ideal for set-top boxes (STBs), portable DVD players, and portable media players (PMPs). The inputs can be directly connected to the digital-to-analog converter (DAC) outputs. The reconstruction filter removes high-frequency signals above 6.75MHz. The amplifiers have 6dB of gain, and the outputs can be DC-coupled to a load of  $75\Omega$ . which is equivalent to two video loads, or it can be AC-coupled to a load of  $150\Omega$ .

The SmartSleep circuitry intelligently reduces power consumption based on the presence of the input signal and the output loads. When the MAX9508 does not detect the presence of sync on the input video signal, the supply current is reduced to less than 7µA. The device only enables a video amplifier when there is an active video input signal and an attached load. The video amplifier remains on while a load is connected. If the load is disconnected, the video amplifier is turned off.

The MAX9508 contains three reconstruction filters, four video amplifiers, and a pulldown switch at one of the two CVBS outputs. The MAX9508 has the ability to control the bidirectional video signals at the CVBS video connections without the need for separate switches or relays. This feature is particularly useful for portable DVD players, which often use the same connector to drive a composite video output and to accept an external video signal to display on the LCD panel.

The MAX9508 operates from a 2.7V to 3.6V single supply and is offered in a small 16-pin TQFN (3mm x 3mm) package. The device is specified over the -40°C to +125°C automotive temperature range.

#### **Applications**

Portable DVD Players Set-Top Boxes (STBs) Portable Set-Top Boxes/ Personal Video Recorders (PVRs) Portable Media Players (PMPs) Portable Applications

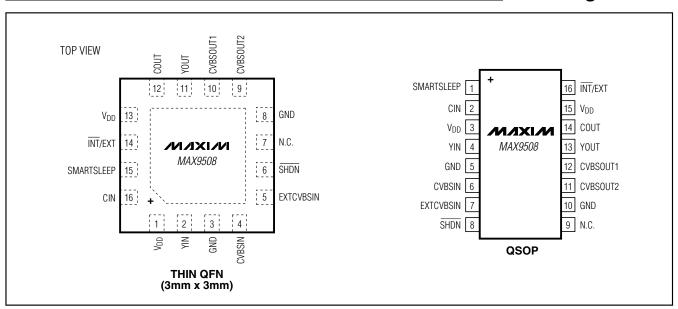

Pin Configurations appear at end of data sheet.

#### **Features**

- ♦ SmartSleep Feature Detects Input Signal and **Output Load Status to Reduce Power** Consumption

- **♦ Triple Standard-Definition Video Reconstruction** Filters with 6.75MHz Passband

- **♦ Luma, Chroma, and Composite Inputs**

- ♦ Luma, Chroma, and Two Composite Outputs

- ♦ Integrated Support for a Bidirectional Composite Video Signal

- ♦ Supports Two Video Loads at Each Output (DC-Coupled)

- ♦ 2.7V to 3.6V Single-Supply Operation

#### **Ordering Information**

| PART         | PIN-PACKAGE                 | PKG CODE | TOP MARK |

|--------------|-----------------------------|----------|----------|

| MAX9508ATE+  | 16 TQFN-EP**<br>(3mm x 3mm) | T1633-4  | AEM      |

| MAX9508AEE+* | 16 QSOP                     | E16-4    | _        |

**Note:** All devices are specified over the -40°C to +125°C operating temperature range.

- +Denotes lead-free package.

- \*Future product—contact factory for availability.

- \*\*EP = Exposed pad.

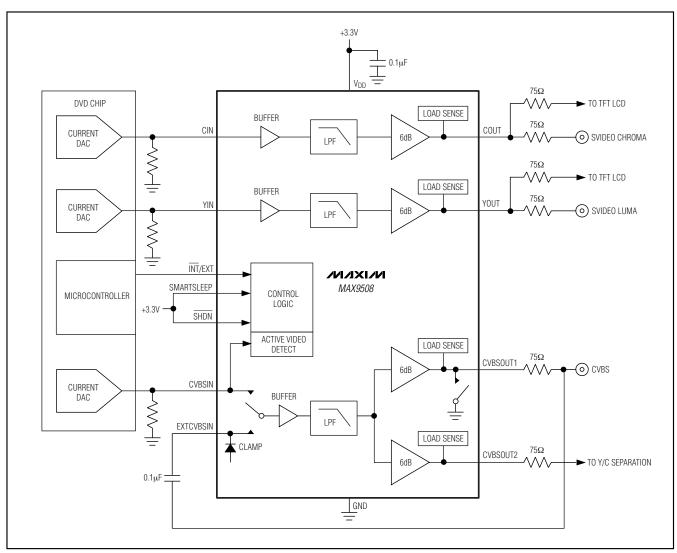

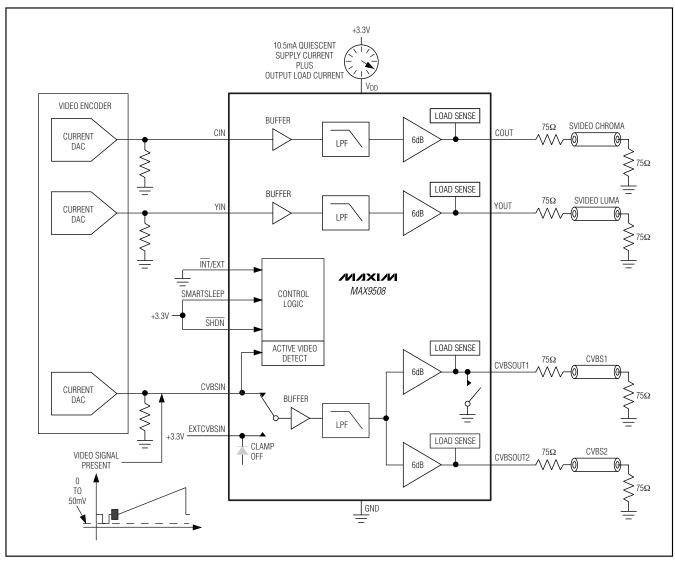

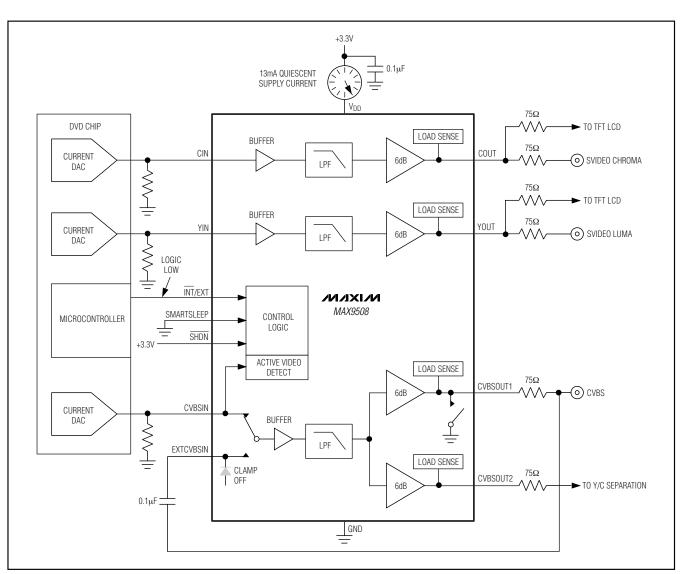

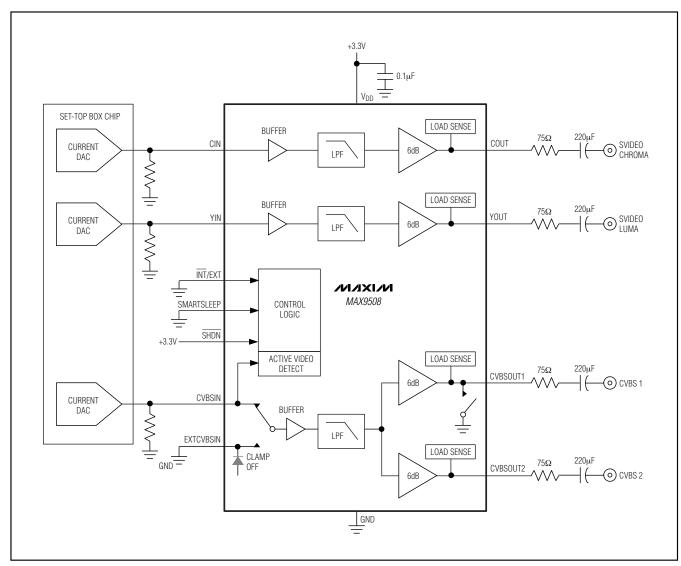

#### **Block Diagrams**

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages with respect to GND.)            |              |

|--------------------------------------------|--------------|

| VDD                                        | -0.3V to +4V |

| SMARTSLEEP, SHDN, INT/EXT                  |              |

| CIN, YIN, CVBSIN, EXTCVBSIN                | -0.3V to +4V |

| Duration of COUT, YOUT, CVBSOUT1, CVBSOUT2 |              |

| Short Circuit to VDD or GND                | .Continuous  |

| Continuous Input Current                   |              |

| CIN, YIN, EXTCVBSIN, CVBSIN,               |              |

| SMARTSLEEP, SHDN, INT/EXT                  | ±20mA        |

| Continuous Power Dissipation (TA = +70°C)  |           |

|--------------------------------------------|-----------|

| 16-Pin TQFN (derate 15.6mW/°C above +70°C) | 1250mW    |

| 16-Pin QSOP (derate 8.3mW/°C above +70°C)  | 667mW     |

| Operating Temperature Range40°C            | to +125°C |

| Junction Temperature                       | +150°C    |

| Storage Temperature Range65°C              | to +150°C |

| Lead Temperature (soldering, 10s)          | +300°C    |

|                                            |           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{\overline{SHDN}} = 3.3V, V_{SMARTSLEEP} = V_{\overline{INT}/EXT} = GND = 0V, R_L = No load. T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 1)$

| PARAMETER                    | SYMBOL          | CONDI                                                                 | MIN                    | TYP   | MAX  | UNITS |                   |

|------------------------------|-----------------|-----------------------------------------------------------------------|------------------------|-------|------|-------|-------------------|

| Supply Voltage Range         | V <sub>DD</sub> | Guaranteed by PSRR                                                    | 2.7                    |       | 3.6  | V     |                   |

|                              |                 | INT/EXT = GND (4 cha<br>YIN = CVBSIN = 0.3V,                          | ,                      |       | 13   | 16    | mA                |

| Supply Current               |                 | INT/EXT = V <sub>DD</sub> (1 char<br>EXTCVBSIN is unconn              | *                      |       | 4.3  | 6     | 1117 (            |

|                              | IDD             | SMARTSLEEP = V <sub>DD</sub> ,<br>CVBSIN has no active                | video signal           |       | 7    | 14    |                   |

|                              |                 | SMARTSLEEP = V <sub>DD</sub> ,<br>burst video signal with<br>(Note 2) |                        | 17    |      | μА    |                   |

| Shutdown Supply Current      | ISHDN           | V <del>SHDN</del> = GND                                               |                        |       | 0.01 | 10    | μΑ                |

| SMARTSLEEP CHARACTERIST      | ICS             |                                                                       |                        |       |      |       |                   |

| Minimum Line Frequency       |                 | CVBSIN                                                                |                        | 14.3  |      |       | kHz               |

| Sync Slice Level             |                 | CVBSIN                                                                |                        | 4.1   |      | 5.2   | % V <sub>DD</sub> |

| Output Load Detect Threshold |                 | Sync pulse present, R                                                 | to GND                 |       |      | 200   | Ω                 |

| DC CHARACTERISTICS           |                 |                                                                       |                        |       |      |       |                   |

| Input Voltage Pange          | VIN             |                                                                       | $2.7V < V_{DD} < 3.6V$ | 0     |      | 1.05  | V                 |

| Input-Voltage Range          |                 | guaranteed by output voltage swing                                    | $3.0V < V_{DD} < 3.6V$ | 0 1.2 |      | 1.2   | ]                 |

| Input Current                | I <sub>IN</sub> | CIN = YIN = CVBSIN =                                                  |                        | 2     | 5    | μΑ    |                   |

| Input Resistance             | R <sub>IN</sub> | CIN, YIN, CVBSIN                                                      |                        | 20    |      | МΩ    |                   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{\overline{SHDN}} = 3.3V, V_{SMARTSLEEP} = V_{\overline{INT}/EXT} = GND = 0V, R_L = No load. T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                          | SYMBOL         | CONDITIONS                                                                                                                                                                                                                                                      |                       |                                         | MIN   | TYP  | MAX   | UNITS            |

|------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------|-------|------|-------|------------------|

| Sync-Tip Clamp Level               | VCLP           | EXTCVBSIN                                                                                                                                                                                                                                                       |                       |                                         | 0.25  |      | 0.37  | V                |

| Input Clamping Current             |                | EXTCVBSIN = 500                                                                                                                                                                                                                                                 | 0mV + V               | V <sub>CLP</sub>                        | 0.5   | 1    | 1.5   | μΑ               |

| EVTOVDOIN Invest Vallage Day       |                | Guaranteed by                                                                                                                                                                                                                                                   | 2.7V                  | < V <sub>DD</sub> < 3.6V                |       |      | 1.05  | M                |

| EXTCVBSIN Input Voltage Range      |                | output voltage swing                                                                                                                                                                                                                                            | 3.0V                  | < V <sub>DD</sub> < 3.6V                |       |      | 1.2   | V <sub>P-P</sub> |

| Sync Crush                         |                | EXTCVBSIN, percentage reduction in sync pulse (0.3V <sub>P-P</sub> ), guaranteed by input clamping current measurement, measured at input                                                                                                                       |                       |                                         |       |      | 2     | %                |

| Maximum Input Source<br>Resistance |                | EXTCVBSIN                                                                                                                                                                                                                                                       |                       |                                         |       | 300  |       | Ω                |

| DC Voltage Gain                    | A <sub>V</sub> | $R_L = 150\Omega$ to $V_{DD}/2$ , $0V \le V_{IN} \le 1.05V$ , $V_{DD} = 2.7V$                                                                                                                                                                                   |                       |                                         | 5.7   | 6    | 6.3   | dB               |

| DC Gain Matching                   |                | $R_L = 150\Omega$ to $V_{DD}/2$ , $0V \le V_{IN} \le 1.05V$ , $V_{DD} = 2.7V$                                                                                                                                                                                   |                       |                                         | -0.2  | 0    | +0.2  | dB               |

|                                    |                | $\begin{split} & \underline{YIN} = CVBSIN = CIN = 0V, \\ & \overline{INT}/EXT = GND, R_L = 150\Omega \text{ to GND} \\ & \underline{C_{EXTCVBSIN}} = 0.1 \mu F \text{ to GND}, \\ & \overline{INT}/EXT = V_{DD}, R_L = 150\Omega \text{ to GND} \\ \end{split}$ |                       | 0.21                                    | 0.3   | 0.38 | V     |                  |

| Output Level                       |                |                                                                                                                                                                                                                                                                 |                       | 0.21                                    | 0.27  | 0.38 | V     |                  |

|                                    |                | Measured at outpo                                                                                                                                                                                                                                               | αι,                   | $T_A = -40^{\circ}C$ to $+85^{\circ}C$  | 2.027 | 2.1  | 2.163 |                  |

|                                    |                | $0V \le V_{IN} \le 1.05V$ ,<br>$R_L = 150\Omega$ to -0.2                                                                                                                                                                                                        |                       | $T_A = -40^{\circ}C$ to $+125^{\circ}C$ | 2.006 |      | 2.163 |                  |

|                                    |                | Measured at output<br>0V ≤ V <sub>IN</sub> ≤ 1.05V,                                                                                                                                                                                                             |                       |                                         | 2.027 | 2.1  | 2.163 |                  |

| Output Voltage Swing               |                | Measured at outpo                                                                                                                                                                                                                                               |                       | $T_A = -40^{\circ}C$ to $+85^{\circ}C$  | 2.316 | 2.4  | 2.472 | V <sub>P-P</sub> |

|                                    |                | $0V \le V_{IN} \le 1.2V$ ,<br>$R_L = 150\Omega$ to -0.2                                                                                                                                                                                                         |                       | $T_A = -40^{\circ}C$ to $+125^{\circ}C$ | 2.292 |      | 2.472 |                  |

|                                    |                | Measured at output, $V_{DD} = 3V$ , $0V \le V_{IN} \le 1.2V$ , $R_L = 150\Omega$ to $V_{DD}$ / 2                                                                                                                                                                |                       |                                         | 2.316 | 2.4  | 2.472 |                  |

|                                    |                | Measured at output<br>0V ≤ V <sub>IN</sub> ≤ 1.05V,                                                                                                                                                                                                             |                       |                                         | 2.027 | 2.1  | 2.163 |                  |

| Output Resistance                  | Rout           | V <sub>OUT</sub> = 1.3V, -5m/                                                                                                                                                                                                                                   | A ≤ I <sub>LO</sub> , | <sub>AD</sub> ≤ +5mA                    |       | 0.47 |       | Ω                |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{\overline{SHDN}} = 3.3V, V_{SMARTSLEEP} = V_{\overline{INT}/EXT} = GND = 0V, R_L = No load. T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 1)

| PARAMETER                    | SYMBOL          | CONDITIONS                                                                          | MIN                      | TYP  | MAX                      | UNITS |

|------------------------------|-----------------|-------------------------------------------------------------------------------------|--------------------------|------|--------------------------|-------|

| Power-Supply Rejection Ratio | PSRR            | $2.7V \le V_{DD} \le 3.6V$ , input referred,<br>R <sub>L</sub> = $150\Omega$ to GND | 48                       |      |                          | dB    |

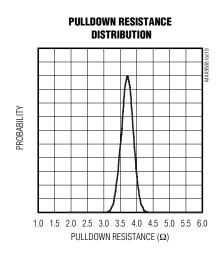

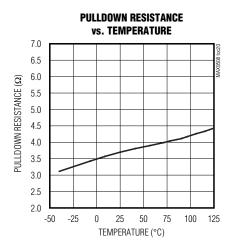

| Output Pulldown Resistance   | R <sub>PD</sub> | INT/EXT = V <sub>DD</sub> , CVBSOUT1                                                |                          | 3.7  |                          | Ω     |

| Output Shutdown Impedance    |                 |                                                                                     |                          | 28   |                          | kΩ    |

| LOGIC INPUTS (SMARTSLEEP,    | SHDN, INT/EX    | (T)                                                                                 |                          |      |                          |       |

| Logic-Low Threshold          | VIL             |                                                                                     |                          |      | 0.3 x<br>V <sub>DD</sub> | V     |

| Logic-High Threshold         | VIH             |                                                                                     | 0.7 x<br>V <sub>DD</sub> |      |                          | V     |

| Logic Input Current          | IIL / IIH       | V <sub>I</sub> = 0V or V <sub>DD</sub>                                              |                          | 0.01 | 10                       | μΑ    |

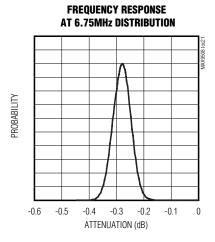

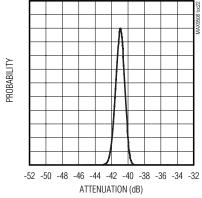

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{\overline{SHDN}} = 3.3V, V_{SMARTSLEEP} = V_{\overline{INT}/EXT} = GND = 0V, R_L = 150\Omega$  to GND.  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                   | SYMBOL | COND                                                                                                      | ITIONS  | }                         | MIN  | TYP  | MAX | UNITS   |

|-----------------------------|--------|-----------------------------------------------------------------------------------------------------------|---------|---------------------------|------|------|-----|---------|

|                             |        |                                                                                                           | f = 5.5 | f = 5.5MHz                |      | -0.1 |     |         |

| Standard-Definition         |        | Inputs are 1V <sub>P-P</sub> , reference                                                                  | f = 6.  | 75MHz                     | -1   | -0.3 | +1  | -10     |

| Reconstruction Filter       |        | frequency is 1MHz.                                                                                        | f = 11  | MHz                       |      | -3   |     | dB      |

|                             |        |                                                                                                           | f = 27  | MHz                       | -33  | -41  |     |         |

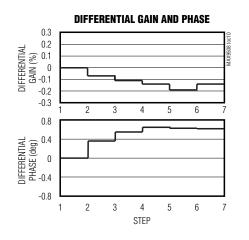

| Differential Oair           | D0     | DC-coupled output,<br>5-step modulated staircase                                                          |         | f = 3.58MHz or<br>4.43MHz |      | 0.2  |     | 0/      |

| Differential Gain           | DG     | AC-coupled output,<br>5-step modulated staircase                                                          |         | f = 3.58MHz or<br>4.43MHz | 0.4  |      |     | %       |

|                             |        | DC-coupled output, 5-step modulated staircase  AC-coupled output, 5-step modulated staircase              |         | upled output, f = 3.58MHz |      | 0.62 |     |         |

| Differential Phase          | DP     |                                                                                                           |         | f = 4.43MHz               |      | 0.75 |     | Dograda |

| Differential Priase         | DP     |                                                                                                           |         | f = 3.58MHz               |      | 0.78 |     | Degrees |

|                             |        |                                                                                                           |         | f = 4.43MHz               | 1.01 |      |     |         |

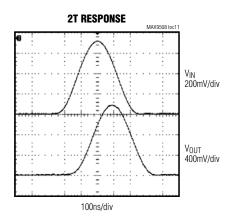

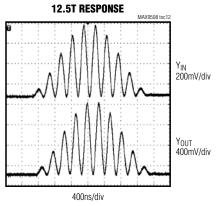

| 2T Pulse Response           |        | 2T = 200ns or 250ns                                                                                       |         |                           |      | 0.2  |     | K%      |

| 2T Bar Response             |        | Bar time is 18µs, the beginning 2.5% and the ending 2.5% of the bar time are ignored, 2T = 200ns or 250ns |         |                           | 0.2  |      | K%  |         |

| 2T Pulse-to-Bar K<br>Rating |        | Bar time is 18µs, the beginnir of the bar time are ignored, 2                                             | -       | _                         |      | 0.3  |     | K%      |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{\overline{SHDN}} = 3.3V, V_{SMARTSLEEP} = V_{\overline{INT}/EXT} = GND = 0V, R_L = 150\Omega$  to GND.  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                    | SYMBOL | CONDITIONS                                                                                                       | MIN | TYP | MAX | UNITS |

|----------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Nonlinearity                                 |        | 5-step staircase                                                                                                 |     | 0.1 |     | %     |

| Interchannel Timing Error                    |        | Difference in time between the 50% point of the output signals, YOUT to COUT                                     |     | 0.2 |     | ns    |

| Group Delay<br>Distortion                    |        | 100kHz ≤ f ≤ 5MHz, inputs are 1V <sub>P-P</sub>                                                                  |     | 10  |     | ns    |

| Interchannel Group<br>Delay Distortion Error |        | Inputs are 1V <sub>P-P</sub>                                                                                     |     | 2   |     | ns    |

| Peak Signal to RMS<br>Noise                  |        | 100kHz ≤ f ≤ 5MHz, inputs are 1V <sub>P-P</sub>                                                                  |     | 67  |     | dB    |

| Power-Supply<br>Rejection Ratio              |        | f = 100kHz, 200mV <sub>P-P</sub> , input referred                                                                |     | 43  |     | dB    |

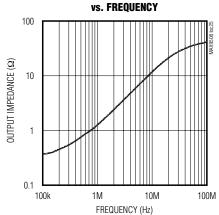

| Output Impedance                             |        | f = 5MHz                                                                                                         |     | 6   |     | Ω     |

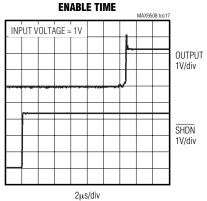

| Enable Time                                  |        | YIN = 1V, output settled to within 1% of the final voltage, $R_L = 150\Omega$ to GND                             |     | 13  |     | μs    |

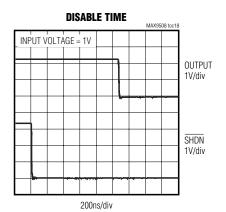

| Disable Time                                 |        | YIN = 1V, output settled to within 1% of the final voltage, $R_L = 150\Omega$ to GND                             |     | 1.1 |     | μs    |

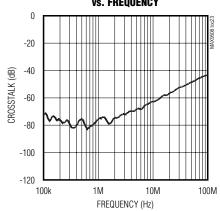

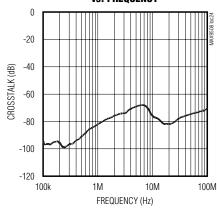

| CROSSTALK                                    |        |                                                                                                                  |     |     |     |       |

| All Hostile Output<br>Crosstalk              |        | f = 4.43MHz                                                                                                      |     | -70 |     | dB    |

| All Hostile Input<br>Crosstalk               |        | $f = 4.43 \text{MHz}, \overline{\text{SHDN}} = \text{GND}, \\ \text{input termination resistors are } 75 \Omega$ |     | -69 | _   | dB    |

Note 1: All devices are 100% production tested at T<sub>A</sub> = +25°C. Specifications over temperature limits are guaranteed by design.

Note 2: Specified current is an average over time.

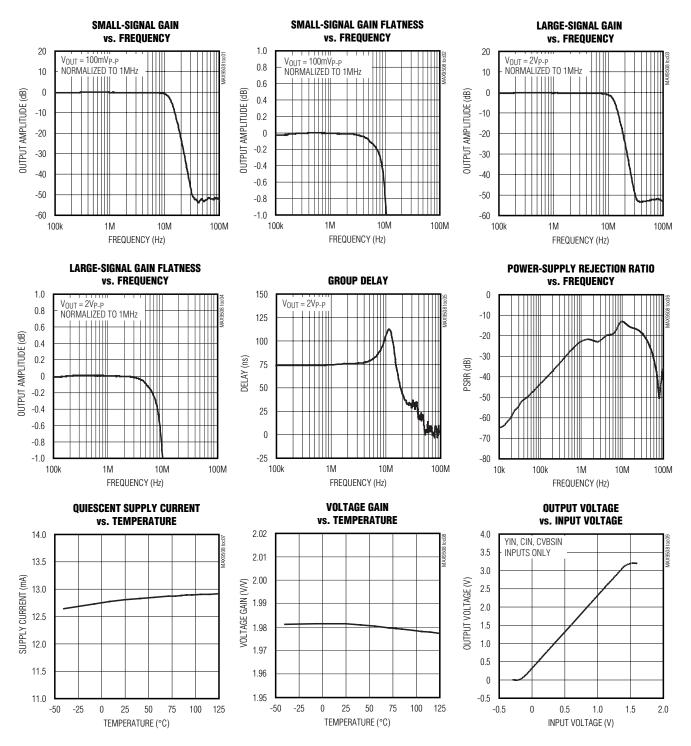

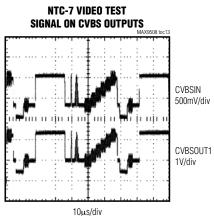

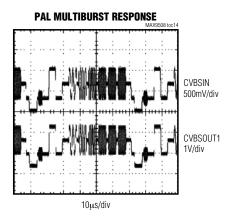

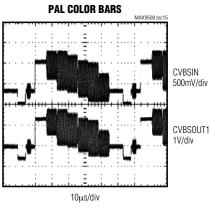

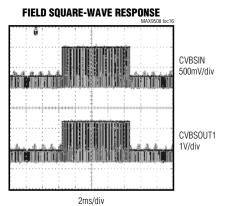

### Typical Operating Characteristics

$(V_{DD} = V_{\overline{SHDN}} = +3.3V, V_{SMARTSLEEP} = V_{\overline{INT}/EXT} = GND = 0V. R_L = 150\Omega$  to GND.  $T_A = +25^{\circ}C$ , unless otherwise noted.)

#### Typical Operating Characteristics (continued)

$(V_{DD} = V_{\overline{SHDN}} = +3.3V, V_{\overline{SMARTSLEEP}} = V_{\overline{INT}/EXT} = GND = 0V. R_L = 150\Omega$  to GND.  $T_A = +25^{\circ}C$ , unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(V_{DD} = V_{\overline{SHDN}} = +3.3V, V_{\overline{SMARTSLEEP}} = V_{\overline{INT}/EXT} = GND = 0V. R_L = 150\Omega$  to GND.  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# OUTPUT-TO-OUTPUT CROSSTALK vs. FREQUENCY

### OUTPUT IMPEDANCE

### Pin Description

| PIN   |       | NAME            | FUNCTION                                                                                                                                                                          |

|-------|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN  | QSOP  | NAME            | FUNCTION                                                                                                                                                                          |

| 1, 13 | 3, 15 | V <sub>DD</sub> | Power Supply. Bypass V <sub>DD</sub> with a 0.1µF capacitor to ground.                                                                                                            |

| 2     | 4     | YIN             | Luma Video Input. Directly connect this input to the video DAC output.                                                                                                            |

| 3, 8  | 5, 10 | GND             | Ground                                                                                                                                                                            |

| 4     | 6     | CVBSIN          | Internal CVBS Signal Input. Directly connect this input to the video DAC output.                                                                                                  |

| 5     | 7     | EXTCVBSIN       | External CVBS Signal Input. AC-couple the signal through a 0.1µF capacitor to this input.                                                                                         |

| 6     | 8     | SHDN            | Active-Low Shutdown Logic Input. Connect to logic low to place device in shutdown.  Connect to logic high for normal operation.                                                   |

| 7     | 9     | N.C.            | No Connection. Connect to GND.                                                                                                                                                    |

| 9     | 11    | CVBSOUT2        | CVBS Output 2                                                                                                                                                                     |

| 10    | 12    | CVBSOUT1        | CVBS Output 1. CVBSOUT1 is actively pulled to GND when INT/EXT is logic high.                                                                                                     |

| 11    | 13    | YOUT            | Luma Video Output                                                                                                                                                                 |

| 12    | 14    | COUT            | Chroma Video Output                                                                                                                                                               |

| 14    | 16    | ĪNT/EXT         | Internal/External CVBS Logic Input. Connect INT/EXT low to process CVBS video signals from CVBSIN input. Connect INT/EXT high to process CVBS video signals from EXTCVBSIN input. |

| 15    | 1     | SMARTSLEEP      | SmartSleep Logic Input. Connect to logic high to activate SmartSleep operation.                                                                                                   |

| 16    | 2     | CIN             | Chroma Video Input. Directly connect this input to the video DAC output.                                                                                                          |

| EP    |       | EP              | Exposed Pad. Connect EP to GND. EP is also internally connected to GND.                                                                                                           |

Figure 1. Typical Application Circuit for Portable DVD Player

### Detailed Description

In the typical application circuit for a portable DVD player (Figure 1), the current DACs on a DVD decoder chip generate video signals. When the internal signal sources are selected, the MAX9508 filters those signals and then drives the video connectors through a  $75\Omega$  back termination resistor. When external video sources are selected, the MAX9508 selects the external composite video signal (EXTCVBSIN), filters, and amplifies it. The output stages of the amplifiers connected to

COUT, YOUT, and CVBSOUT1 become high impedance. The n-channel switch at CVBSOUT1 turns on, thereby converting the back termination resistor into an input termination resistor.

#### SmartSleep Feature

The SmartSleep feature is activated when the SMARTSLEEP input is connected to logic high. The SmartSleep feature provides intelligent power management by selectively disabling the filters and output amplifiers based on the presence of video signals or loads attached to the

10 \_\_\_\_\_\_\_/VIXI/VI

outputs. If the SmartSleep feature is not activated and the part is not in shutdown, the filters and output amplifiers completely turn on, regardless of whether there is a video signal at the CVBSIN input and whether there are loads connected at the outputs.

SmartSleep only works with DC-coupled loads.

#### Standby Mode

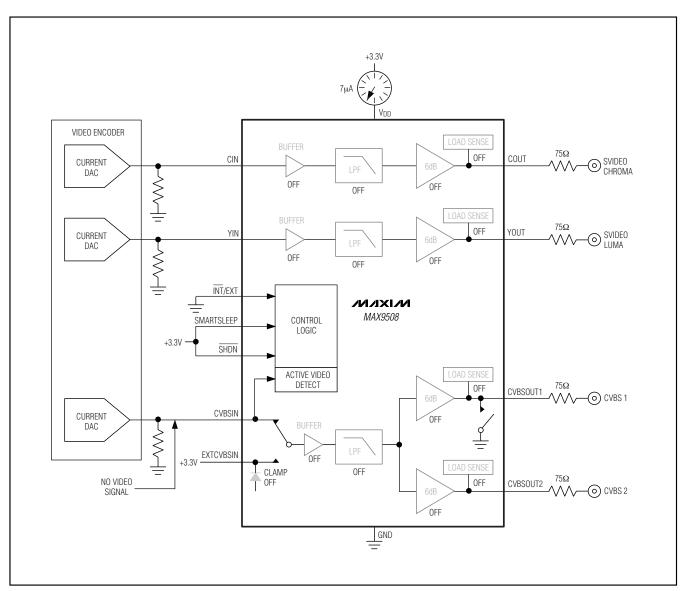

In standby mode, the filters and output amplifiers are off and only the active video detect circuit is operational. Quiescent current consumption is approximately 7µA (Figure 2). The active video detect circuit checks if sync is present on the CVBSIN signal. If no sync is detected the device remains in standby mode.

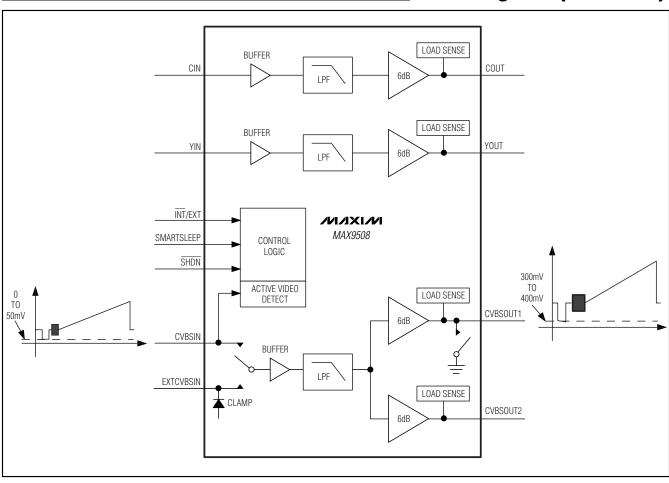

Figure 2. Standby Mode

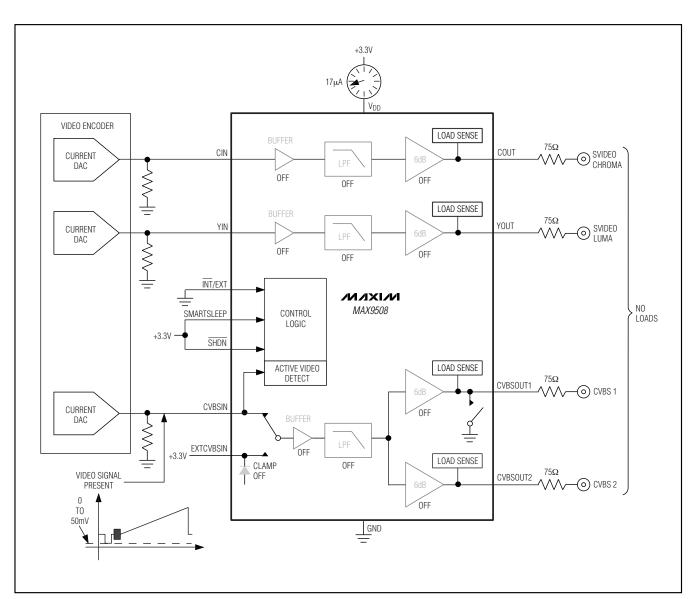

#### **Active-Detect Mode**

The active video detect circuit slices the CVBSIN signal at 4.7% of the power supply (155mV for a 3.3V supply). If the transitions occur at a rate of 14.3kHz or higher, a video signal is present. When the MAX9508 detects a video signal with sync at the CVBSIN input, the control logic enters the active-detect mode and enables the load sense circuitry (Figure 3). The supply current is typically  $17\mu\text{A}$ .

If an output load is not connected to any amplifier, the MAX9508 remains in active detect mode. Eight times per second, each load-sense circuit checks for a load by connecting an internal  $15k\Omega$  pullup resistor to the output for 1ms. If the output is pulled up, then no load is present. If the output stays low, a load is connected.

Figure 3. Active-Detect Mode with No Output Loads

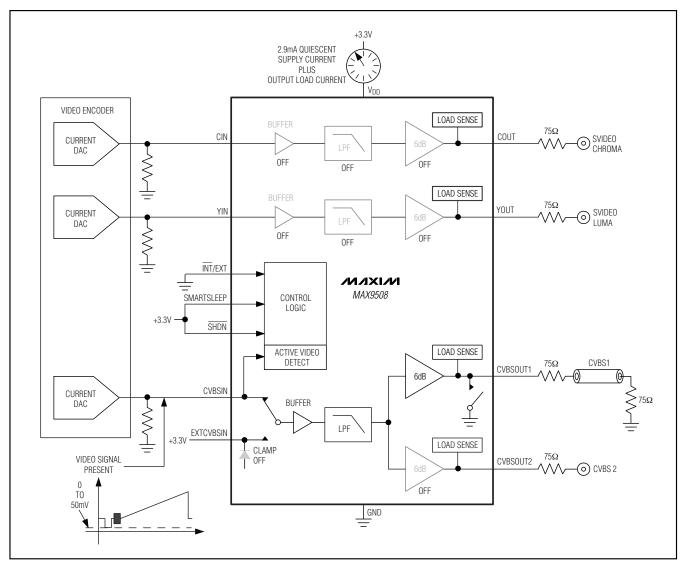

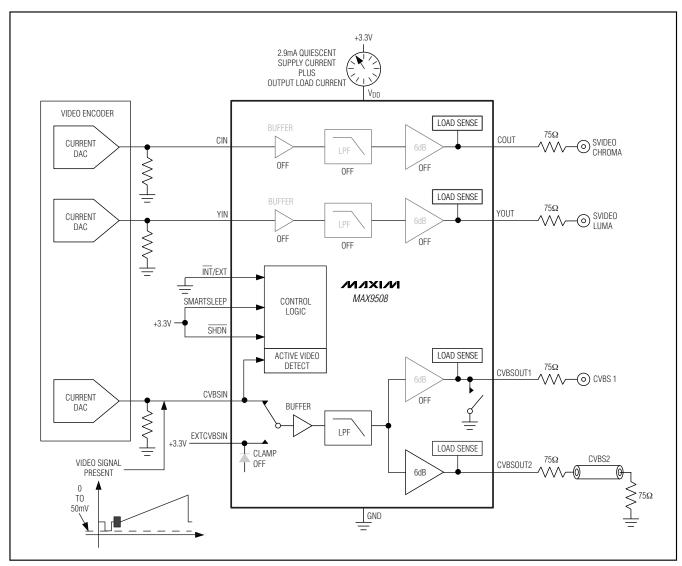

#### Full-Operation Mode

If a load is connected to an output, the corresponding filter and amplifier turn on and remain on until the output load is disconnected. In full-operation mode, SmartSleep intelligently reduces the supply current based on the input signal presence and output loading. Figures 4, 5, and 6 show which portions of the MAX9508 turn on and which remain off with different load configurations.

When an amplifier is on, it continually checks if the load has been disconnected by detecting if the amplifier output is sourcing current during a horizontal line time. If no sourcing current is detected within one horizontal line time (approximately 64µs), the load has been disconnected and the amplifier returns to active-detect mode. If, at any time, the input video signal is removed, the MAX9508 returns to standby mode.

If the SmartSleep feature is not activated and the part is not in shutdown, the filters and amplifiers completely turn on, regardless of whether there is a video signal at the CVBSIN input and whether there are loads connected at the outputs.

Figure 4. Full-Operation Mode with CVBSOUT1 Loaded

Figure 5. Full-Operation Mode with CVBSOUT2 Loaded

Figure 6. Full-Operation Mode with All Outputs Loaded

# Internal Mode Versus External Mode Internal Mode

Set the INT/EXT control input low for internal mode. The MAX9508 processes video signals from an internal

source such as a DVD chip (Figure 7). The 2:1 multiplexer selects the video signal on CVBSIN. The EXTCVBSIN video signal is ignored.

Figure 7. Internal Mode Operation for Portable DVD Applications

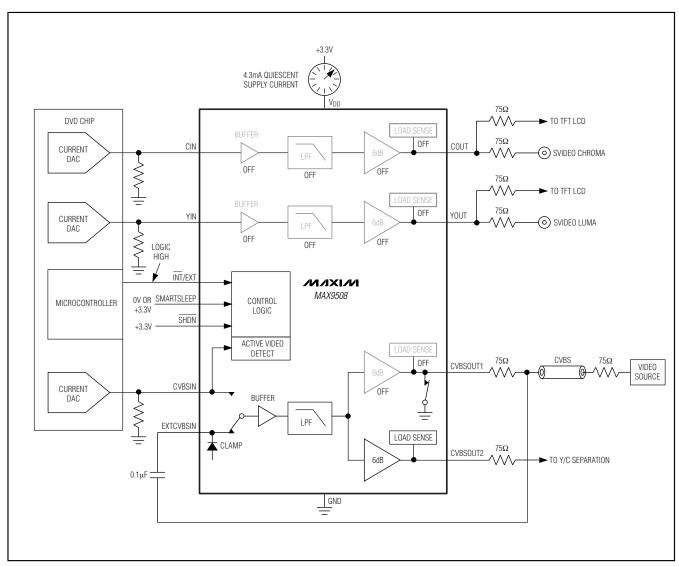

#### External Mode

Set the INT/EXT control input high for external mode. The 2:1 multiplexer selects the video signal on EXTCVBSIN (Figure 8). The YIN, CIN, and CVBSIN sig-

nals are ignored. The block drawing of the MAX9508 in Figure 8 shows which circuits are off while in external mode. SmartSleep does not function in external mode, and the SMARTSLEEP input is ignored.

Figure 8. External Mode Operation for Portable DVD Applications

#### Inputs

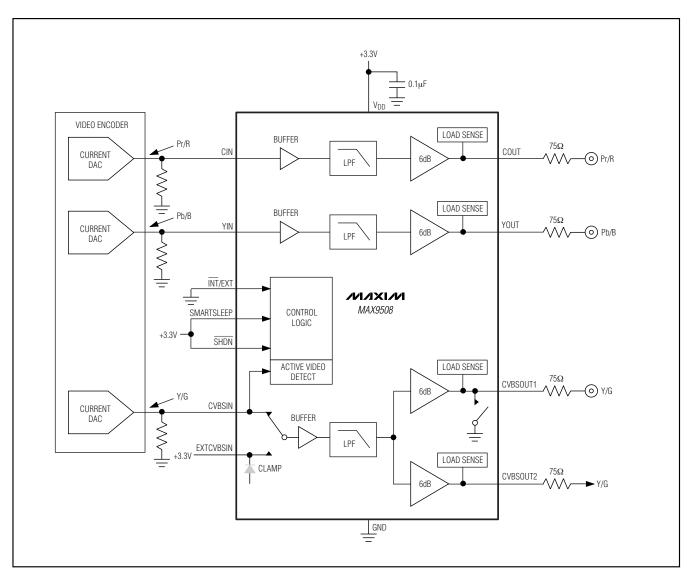

The MAX9508 video inputs YIN, CIN, and CVBSIN should be directly connected to the output of the video current DAC. DC-coupling ensures that the input signals are ground referenced such that the sync tip of composite or luma signals is within 50mV of ground and the blank level of the chroma signal is between 0.5V and 0.65V. Since the input buffer is identical for YIN, CIN, and CVBSIN, any standard-definition video signal can be applied to those inputs as long as the signal is between ground and 1.05V when VDD = 2.7V. For example, three composite video signals could be

applied to YIN, CIN, and CVBSIN. The RGB set and the YPbPr set can also be inputs to YIN, CIN, and CVBSIN (Figure 9).

The EXTCVBSIN input can only handle signals with a sync pulse, such as composite, video, or luma. Because the DC level of an external video input signal is unknown, the external video signal is AC-coupled through a 0.1  $\mu$ F capacitor, and a sync tip clamp sets the internal DC level of the MAX9508. A 2:1 multiplexer under the control of the  $\overline{\rm INT}/\rm EXT$  input selects either the signal at CVBSIN or EXTCVBSIN.

Figure 9. Y, Pr, Pb or RGB Set Applied to MAX9508

#### **Video Reconstruction Filter**

The MAX9508 filter passband is 6.75MHz, which makes the device suitable for the higher bandwidth video signals from a DVD chip. Broadcast video signals actually require less bandwidth because of channel limitations: NTSC signals have a 4.2MHz bandwidth, and PAL signals have a 5MHz bandwidth. Video signals from a DVD player are not channel limited; therefore, the bandwidth of DVD video signals can push right against the Nyquist limit of 6.75MHz. (Recommendation ITU-R BT.601-5 specifies 13.5MHz as the sampling rate for standard-definition video). Therefore, the maximum bandwidth of the signal is 6.75MHz. To ease the filtering requirements, most modern video systems oversample by two times, clocking the video current DAC at 27MHz.

#### **Outputs**

The video output amplifiers can both source and sink load current, allowing output loads to be DC- or AC-coupled. The amplifier output stage needs about 300mV of headroom from either supply rail. The MAX9508 has an internal level-shift circuit that positions the sync tip at approximately 300mV at the output. The blank level of the chroma output is positioned at approximately 1.3V if the blank level of the chroma input signal is 0.5V. The blank level of the chroma output is positioned at approximately 1.5V if the blank level of the chroma input signal is 0.6V.

If the supply voltage is greater than 3.135V (5% below a 3.3V supply), each amplifier can drive two DC-coupled video loads to ground. If the supply is less than 3.135V, each amplifier can drive only one DC-coupled or AC-coupled video load.

#### Shutdown

When  $\overline{SHDN}$  is low, the MAX9508 draws typically less than 10nA supply current. All the amplifier outputs become high impedance. The effective output resistance at the video outputs is  $28k\Omega$ , due to the internal feedback resistors to ground.

#### **Applications Information**

# Reducing Power Consumption in the Video DACs

YIN, CIN, and CVBSIN have high-impedance input buffers and can work with source resistances as high as  $300\Omega$ . To reduce power dissipation in the video DACs, the DAC output resistor can be scaled up in value. The reference resistor that sets the reference current inside the video DACs must also be similarly scaled up. For instance, if the output resistor is  $37.5\Omega$ , the DAC must source 26.7mA when the output is 1V. If the output resistor is increased to  $300\Omega$ , the DAC only needs to source 3.33mA when the output is 1V.

There is parasitic capacitance from the DAC output to ground. That capacitance in parallel with the DAC output resistor forms a pole that can potentially roll off the frequency response of the video signal. For example,  $300\Omega$  in parallel with 50pF creates a pole at 10.6 MHz. To minimize this capacitance, reduce the area of the signal trace attached to the DAC output as much as possible, and place the MAX9508 as close to the video DAC outputs as possible.

#### **AC-Coupling the Outputs**

The outputs can be AC-coupled since the output stage can source and sink current as shown in Figure 10. Coupling capacitors should be 220 $\mu\text{F}$  or greater to keep the highpass filter formed by the  $150\Omega$  equivalent resistance of the video transmission line to a corner frequency of 4.8Hz or below. The frame rate of PAL systems is 25Hz, and the frame rate of NTSC systems is 30Hz. The corner frequency should be well below the frame rate. SmartSleep only works with DC-coupled loads.

Figure 10. AC-Coupled Outputs

#### **Power-Supply Bypassing and Ground**

The MAX9508 operates from a single-supply voltage down to 2.7V, allowing for low-power operation. Bypass VDD to GND with a 0.1 $\mu$ F capacitor. Place all external components as close to the device as possible.

### Block Diagrams (continued)

### **Pin Configurations**

\_\_\_\_\_Chip Information

PROCESS: BICMOS

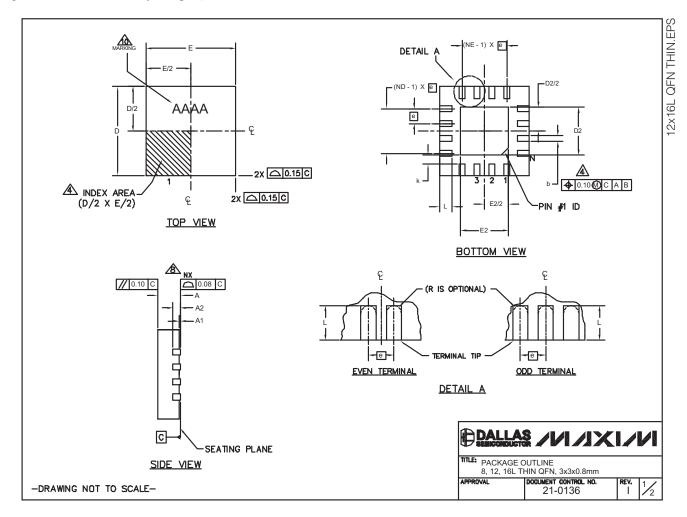

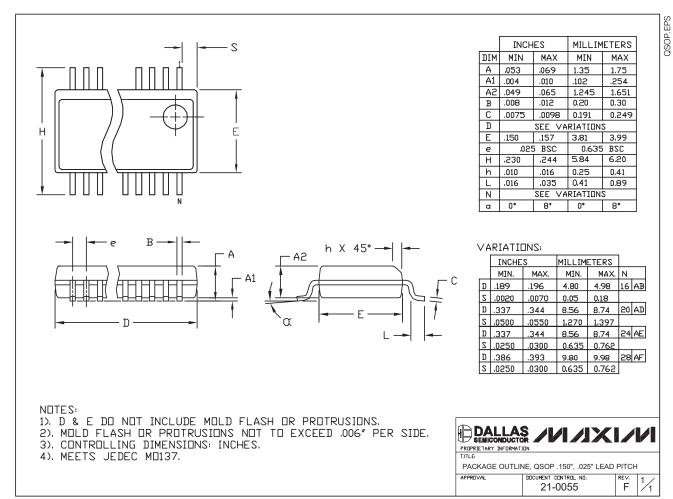

#### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

#### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

| PKG  | 8L 3x3   |         |          | 8L 3x3 12L 3x3 |      |          | 16L 3x3   |      |      |

|------|----------|---------|----------|----------------|------|----------|-----------|------|------|

| REF. | MIN.     | NOM.    | MAX.     | MIN.           | NOM. | MAX.     | MIN.      | NOM. | MAX. |

| Α    | 0.70     | 0.75    | 0.80     | 0.70           | 0.75 | 0.80     | 0.70      | 0.75 | 0.80 |

| b    | 0.25     | 0.30    | 0.35     | 0.20           | 0.25 | 0.30     | 0.20      | 0.25 | 0.30 |

| D    | 2.90     | 3.00    | 3.10     | 2.90           | 3.00 | 3.10     | 2.90      | 3.00 | 3.10 |

| Е    | 2.90     | 3.00    | 3.10     | 2.90           | 3.00 | 3.10     | 2.90      | 3.00 | 3.10 |

| е    | 0.       | .65 BSC | Э.       | 0.50 BSC.      |      |          | 0.50 BSC. |      |      |

| L    | 0.35     | 0.55    | 0.75     | 0.45           | 0.55 | 0.65     | 0.30      | 0.40 | 0.50 |

| N    |          | 8       |          | 12             |      |          |           | 16   |      |

| ND   | 2        |         |          | 3              |      |          |           | 4    |      |

| NE   |          | 2       |          |                | 3    |          |           | 4    |      |

| A1   | 0        | 0.02    | 0.05     | 0              | 0.02 | 0.05     | 0         | 0.02 | 0.05 |

| A2   | 0.20 REF |         | 0.20 REF |                |      | 0.20 REF |           |      |      |

| k    | 0.25     | -       | -        | 0.25           | -    | -        | 0.25      | -    | -    |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |             |        |  |  |  |  |

|------------------------|------|------|------|------|------|------|-------------|--------|--|--|--|--|

| PKG.                   |      | D2   |      |      | E2   |      | PIN ID      | JEDEC  |  |  |  |  |

| CODES                  | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. | PINID       | JEDEC  |  |  |  |  |

| TQ833-1                | 0.25 | 0.70 | 1.25 | 0.25 | 0.70 | 1.25 | 0.35 x 45°  | WEEC   |  |  |  |  |

| T1233-1                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |  |  |  |

| T1233-3                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |  |  |  |

| T1233-4                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |  |  |  |

| T1633-2                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |  |  |  |

| T1633F-3               | 0.65 | 0.80 | 0.95 | 0.65 | 0.80 | 0.95 | 0.225 x 45° | WEED-2 |  |  |  |  |

| T1633FH-3              | 0.65 | 0.80 | 0.95 | 0.65 | 0.80 | 0.95 | 0.225 x 45° | WEED-2 |  |  |  |  |

| T1633-4                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |  |  |  |

| T1633-5                | 0.95 | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |  |  |  |

#### NOTES

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO

JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED

WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR

MARKED FEATURE.

⚠ DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.20 mm AND 0.25 mm FROM TERMINAL TIP.

⚠ ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

& COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

DRAWING CONFORMS TO JEDEC MO220 REVISION C.

MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

11. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

12. WARPAGE NOT TO EXCEED 0.10mm.

PACKAGE OUTLINE 8, 12, 16L THIN QFN, 3x3x0.8mm

PROVAL DOCUMENT CONTROL NO. REV. 2 /

-DRAWING NOT TO SCALE-

#### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### \_Revision History

Pages changed at Rev 1: 1, 2, 4, 7, 8, 11–7, 19, 20

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.